模拟集成电路的分析与设计 从理论到实践的深度解析

模拟集成电路是现代电子系统的核心,其设计与分析是电子工程领域的关键技术之一。与数字集成电路处理离散的0和1信号不同,模拟IC处理的是连续变化的真实世界信号,如声音、光线、温度、压力等。因此,其设计过程更为复杂,对精度、噪声、功耗和线性度的要求极高。本文将系统性地探讨模拟集成电路的分析与设计流程。

一、设计基础与核心概念

模拟集成电路的设计始于对基本模拟模块的深刻理解。核心模块包括:

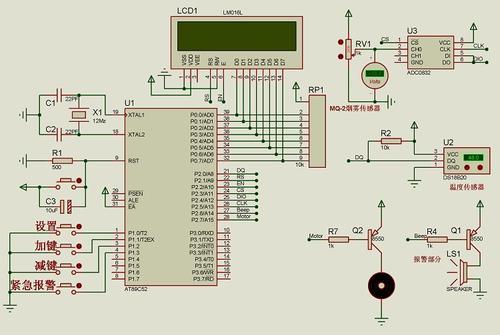

- 单级放大器:如共源、共栅、共漏(源极跟随器)结构,是构建复杂电路的基础。

- 差分放大器:提供高共模抑制比(CMRR),是运放和许多模拟系统的输入级。

- 电流镜与偏置电路:为电路提供稳定、与工艺和温度无关的偏置电流,是模拟IC的“生命线”。

- 输出级:如推挽(Class AB)输出级,负责驱动低阻抗负载并提供足够的电流输出能力。

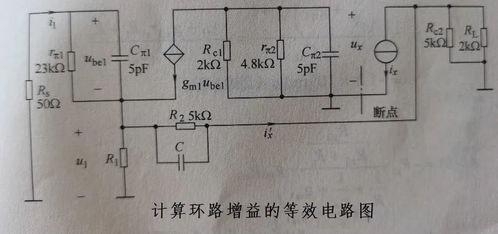

这些模块的分析离不开半导体器件物理(特别是MOSFET或BJT的小信号模型)和电路理论。设计师必须熟练掌握增益、带宽、输入/输出阻抗、噪声、非线性失真(谐波失真、互调失真)和稳定性(相位裕度)等关键性能参数的计算与仿真方法。

二、设计流程:从规范到版图

一个完整的模拟IC设计遵循一套严谨的流程:

- 系统规划与指标定义:明确电路的功能、性能指标(如增益、带宽、功耗、电源电压、面积等)和应用场景。这是设计的“宪法”,所有后续工作都围绕其展开。

- 架构选择与电路设计:根据指标选择合适的电路架构(如运放采用折叠式共源共栅以获得高增益,或采用两级结构以优化速度与功耗)。在晶体管级进行原理图设计,并通过手工计算进行初步尺寸确定。

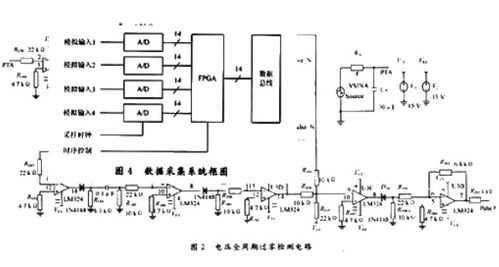

- 电路仿真与迭代优化:利用EDA工具(如Cadence Virtuoso, SPICE)进行深入的仿真验证。这包括:

- 直流分析:确保工作点正确。

- 交流小信号分析:验证增益、带宽和相位裕度。

- 瞬态分析:观察大信号时域响应和建立时间。

- 噪声分析、蒙特卡洛分析和工艺角分析:评估电路的鲁棒性,确保在工艺偏差、温度变化下仍能满足指标。

此阶段需要反复迭代修改晶体管尺寸和拓扑,直至满足所有要求。

- 版图设计与物理实现:将电学原理图转化为实际的硅片几何图形。这是设计中最具挑战性的环节之一,需严格遵守设计规则(DRC),并充分考虑:

- 匹配性:对差分对、电流镜等关键器件采用共质心、叉指等布局技巧以减小失配。

- 寄生效应:精心规划走线以最小化寄生电阻、电容,特别是栅极和敏感高阻抗节点的寄生电容。

- 信号完整性:区分模拟与数字电源/地,采用保护环(Guard Ring)隔离噪声,注意衬底耦合效应。

完成后必须进行版图与原理图对比(LVS)和寄生参数提取后仿真(Post-layout Simulation),以确认版图未引入性能劣化。

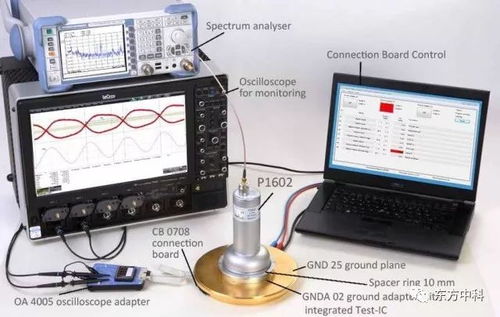

- 流片与测试:将设计好的版图数据(GDSII文件)送交晶圆厂制造。芯片返回后,在测试平台上进行严格的性能测试,并与仿真结果对比,完成设计闭环。

三、关键挑战与前沿趋势

模拟IC设计始终在与物理极限和工程约束作斗争:

- 电源电压降低:随着工艺节点进步,电源电压持续下降,留给晶体管的电压余度(Headroom)越来越小,设计高增益、高摆幅的电路变得异常困难。

- 工艺变异:深亚微米及以下工艺中,器件参数的随机离散性(如阈值电压波动)显著增大,迫使设计必须更加注重鲁棒性和统计设计方法。

- 混合信号集成:在片上系统(SoC)中,模拟模块必须与高速数字电路共存,电磁干扰和衬底噪声耦合成为严峻挑战,隔离技术至关重要。

当前的前沿趋势包括:

- 数据转换器(ADC/DAC)的持续演进:追求更高速度、更高精度和更低功耗,新型架构(如噪声整形SAR ADC)不断涌现。

- 射频(RF)与毫米波集成电路:服务于5G/6G通信,设计频率高达数百GHz的电路。

- 电源管理集成电路(PMIC):为便携设备和高效能计算提供高效、智能的电压转换与功率分配。

- 利用先进封装技术:如硅中介层(Interposer)和芯粒(Chiplet),将不同工艺节点的模拟、数字、射频芯粒集成,实现异构集成。

###

模拟集成电路的分析与设计是一门融合了深厚理论、丰富经验和艺术直觉的学科。它要求设计师不仅精通电路理论、半导体物理和EDA工具,还需对制造工艺和实际应用需求有透彻理解。尽管面临数字化浪潮的冲击,模拟电路作为连接物理世界与数字世界的桥梁,其重要性从未减弱,反而在人工智能、物联网、生物医疗等新兴领域焕发出新的活力。掌握其分析与设计方法,是通往高端芯片设计殿堂的必经之路。

如若转载,请注明出处:http://www.jz876.com/product/27.html

更新时间:2026-04-22 05:48:23