无锁相环电压全周期过零检测电路的仿真与设计 集成电路设计视角

1. 引言

在电力电子、电机驱动、并网逆变器及电能质量监测等诸多领域,电压信号的过零点(Zero-Crossing Point, ZCP)是至关重要的参考信息。传统的过零检测常依赖锁相环(PLL)技术,以实现与电网电压的精确同步。PLL结构复杂,存在动态响应速度、环路稳定性以及高次谐波抑制能力之间的权衡问题,且在频率波动较大或电压畸变严重的场景下性能可能受限。

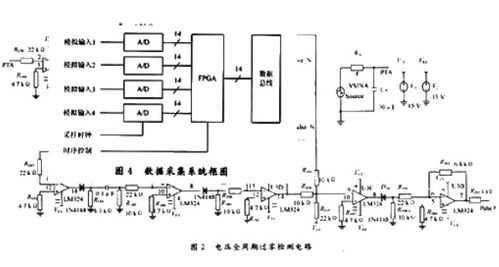

“无锁相环电压全周期过零检测电路”应运而生,它旨在通过更简洁、更鲁棒的模拟或混合信号电路直接提取电压过零信息,尤其适用于对成本、功耗和响应速度有严苛要求的集成电路(IC)设计。本文将从集成电路设计的角度,详细概述此类电路的原理、关键模块设计、仿真验证方法以及相关的设计考量。

2. 核心原理与电路架构

无锁相环过零检测的核心思想是直接对输入的交流电压信号进行处理,无需构建复杂的频率/相位跟踪环路。其典型架构通常包含以下几个关键模块:

1. 信号调理前端:

* 衰减/电平移位网络: 将高压或高摆幅的电网电压(如220V RMS)安全地转换到IC内部可处理的电压范围(如0-5V)。

- 滤波网络: 通常包括低通滤波器,用于抑制高频噪声和毛刺,防止误触发。设计时需在噪声抑制与信号延时(相位滞后)之间取得平衡。

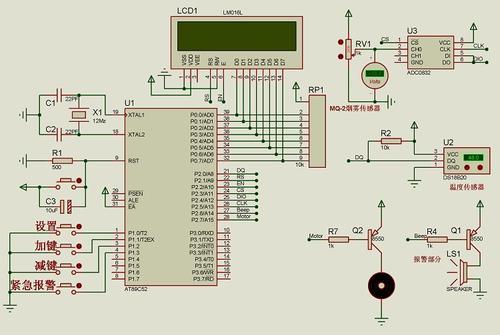

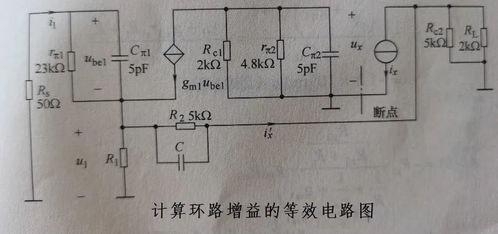

2. 过零比较与检测单元:

* 核心比较器: 这是电路的核心。调理后的交流信号被送入一个高速、高精度的电压比较器。比较器的另一端通常接一个参考电压(例如,系统地GND或一个偏置电压Vref)。当输入信号穿越该参考电平时,比较器输出发生跳变。

- 迟滞(施密特触发器)设计: 为增强抗干扰能力,防止在过零点附近因噪声引起比较器输出振荡,必须引入迟滞。这可以通过在比较器周围配置正反馈电阻网络来实现。迟滞窗口(Hysteresis Window)的大小是设计的关键参数,需根据预期的噪声水平和检测精度来确定。

3. 边沿检测与脉冲整形:

* 比较器输出的跳变沿(上升沿和下降沿)对应正、负半周的过零点。通常使用数字逻辑(如D触发器、与门构成的边沿检测电路)或模拟微分电路来捕捉这些跳变,并生成一个干净、窄脉宽的标准数字脉冲信号(ZCP脉冲),供后续数字系统(如MCU、DSP)使用。

4. 全周期检测逻辑:

* “全周期”意味着需要同时检测正过零点(电压从负到正穿越零点)和负过零点(从正到负穿越零点)。这可以通过以下方式实现:

- 双比较器方案: 使用两个比较器,一个参考地为正过零检测,另一个参考一个微小的正电压(或使用差分比较)来间接检测负过零,再通过逻辑合成。

- 单比较器+逻辑判断方案: 利用原始信号的极性信息(可通过另一个增益为1的反相器通道获得)与比较器输出进行逻辑运算,区分正负过零点。

3. 集成电路设计中的关键考量

在将上述架构集成到单颗芯片时,需重点解决以下问题:

1. 工艺与器件选择:

* 高压工艺: 若前端集成衰减网络,可能需要高压器件(如LDMOS)来承受输入电压。

- 比较器设计: 需设计低失调电压(Offset Voltage)、高共模抑制比(CMRR)、快速响应的比较器。失调电压会直接导致过零点检测误差。采用自动归零(Auto-zeroing)或斩波(Chopper)技术可有效降低失调。

- 噪声管理: 在版图布局上,模拟信号路径需远离数字电源和地线,采用保护环(Guard Ring),合理规划电源去耦。

2. 精度与误差源分析:

* 主要误差源: 比较器失调电压、参考电压的精度与温漂、前端滤波电路引起的相位延迟、迟滞窗口的不对称性。

- 相位补偿: 滤波器和比较器本身会引入固定的相位滞后。在要求绝对相位精度的应用中(如同步整流),需在数字域或通过可调延时线进行补偿。

3. 鲁棒性设计:

* 电压扰动与跌落: 电路需在电压幅值波动、含有谐波或瞬时跌落(Sag)时仍能可靠工作。合理的迟滞和滤波设计是关键。

- 启动与瞬态过程: 确保系统上电或输入电压突变时,电路能快速进入稳定检测状态,避免输出乱脉冲。

4. 仿真验证流程

IC设计离不开 rigorous 的仿真。仿真通常分层次进行:

1. 晶体管级仿真(如使用Cadence Spectre):

* 关键模块验证: 对核心比较器、施密特触发器、滤波放大器等进行DC、AC(带宽、相位)、瞬态(响应速度)和噪声仿真。蒙特卡洛(Monte Carlo)分析用于评估工艺偏差和失配对性能(如失调电压)的影响。

2. 系统级/混合信号仿真:

* 整体功能验证: 搭建包含所有模拟模块和数字逻辑的顶层电路。输入标准的正弦波,以及叠加了噪声、谐波或带有幅值/频率阶跃变化的扰动信号,观察ZCP脉冲输出的准确性、延时和抖动。

- 极端条件测试: 在不同工艺角(FF, TT, SS)、不同温度(-40°C 到 125°C)和电源电压波动下进行仿真,确保全条件覆盖下的功能正确性。

3. 仿真与实测的桥梁——后仿真:

* 在完成版图设计后,提取包含寄生电阻电容(RC)的参数(如DSPF文件),进行后仿真(Post-layout Simulation)。这是最接近芯片实际性能的仿真,用于最终确认时序、速度是否满足要求,以及寄生效应是否引起功能异常。

5. 设计资料与实现

一套完整的设计资料通常包括:

- 设计规格书(Specification): 明确输入电压范围、过零点检测精度(时间或相位误差)、响应时间、功耗、电源电压、工作温度范围等指标。

- 电路原理图与仿真报告: 各级电路图及对应的性能仿真结果。

- 版图(Layout)文件: 符合设计规则(DRC)和电路图一致性(LVS)的物理版图,需特别关注匹配、噪声隔离和可靠性。

- 测试方案(Test Plan): 规划如何在实际硅片上验证电路性能,包括测试板设计、激励信号生成和输出信号测量方法。

6. 与展望

无锁相环电压全周期过零检测电路以其结构简单、响应快速、易于集成的优势,在众多低成本、高可靠性的电源管理和能源转换IC中占据重要地位。成功的IC设计需要深入理解系统需求,精心设计每个模拟子模块,并通过全面的仿真来预测和优化其在实际工艺条件下的性能。随着工艺进步,此类电路可以进一步与数字校准技术结合,实现自校正、自适应迟滞等智能功能,以在更复杂的电网环境下提供更精准、更鲁棒的同步信号。

如若转载,请注明出处:http://www.jz876.com/product/20.html

更新时间:2026-05-08 15:24:54