一种低功耗CMOS过温保护电路的设计

随着集成电路技术的飞速发展,芯片的集成度不断提高,功耗密度也随之增大,导致芯片在工作时更容易产生过热问题。过热不仅会影响电路的性能和可靠性,严重时甚至会永久性损坏芯片。因此,集成高效、可靠的过温保护电路(OTP, Over-Temperature Protection)已成为现代集成电路设计中不可或缺的一环。本文将探讨一种基于标准CMOS工艺的低功耗过温保护电路的设计思路与实现方法。

一、设计目标与原理

本设计的主要目标是实现一个结构简单、功耗低、响应准确且易于集成的过温保护电路。其核心原理是利用半导体器件(如双极晶体管或MOS管)的温度特性来感知芯片温度。最常见的方法是利用双极晶体管的基极-发射极电压(VBE)具有负温度系数(约-2mV/°C),而不同电流密度下的两个双极晶体管的VBE差值(ΔVBE)具有正温度系数。通过将这两个电压信号进行适当组合与比较,可以产生一个与绝对温度成正比(PTAT)的电压。将此PTAT电压与一个带隙基准电压进行比较,当PTAT电压超过设定阈值时,比较器翻转,触发保护信号。

考虑到低功耗需求,本设计将全部采用CMOS器件,并尽可能降低偏置电流。我们采用亚阈值工作的MOS管来构建电流源和核心传感单元,以大幅降低静态电流。

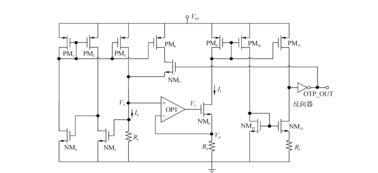

二、电路架构设计

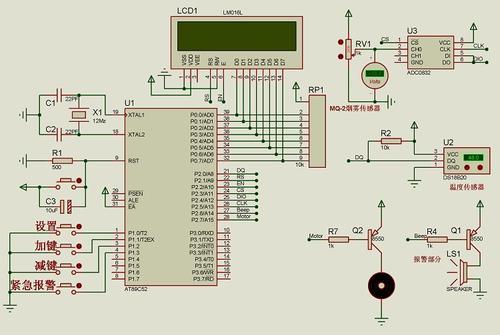

所提出的低功耗CMOS过温保护电路主要由以下几个模块构成:

- 亚阈值偏置电流源:为整个电路提供纳安级(nA)的稳定偏置电流。该电流源利用MOS管在亚阈值区的指数特性,通过电流镜结构产生与电源电压和工艺变化关系较小的基准电流。

- 温度传感核心单元:这是电路的关键部分。我们采用衬底PNP晶体管(在标准CMOS工艺中易于获得)来替代传统的垂直PNP管。两个尺寸不同的衬底PNP管(Q1和Q2)工作在不同的电流密度下。由偏置电流源提供的电流I1和I2(通常I2 = N * I1,N为面积比)分别注入这两个晶体管。由此产生:

- VBE1, 具有负温度系数。

- ΔVBE = VBE1 - VBE2 = (kT/q) * ln(N), 具有正温度系数。

通过电阻网络,将ΔVBE放大,并与经过电平移位的VBE1相加,从而产生一个近似零温度系数的带隙基准电压VREF,以及一个与绝对温度成正比的电压VPTAT。

- 阈值设定与比较器:将VPTAT信号与一个由VREF分压得到的固定阈值电压VTH进行比较。VTH对应着需要触发保护动作的预设温度点(例如125°C)。比较器采用低功耗、高增益的差分放大器结构,并设计适量的迟滞(Hysteresis),以防止在临界温度点附近因噪声引起的输出振荡。迟滞功能可以通过在比较器输出端引入正反馈电阻来实现。

- 输出驱动与整形电路:比较器的输出经过反相器链进行缓冲和整形,产生一个数字化的过温标志信号OTFLAG。当芯片温度低于阈值时,OTFLAG为低电平(例如0);当温度达到或超过阈值时,OT_FLAG翻转为高电平(例如VDD)。该信号可以直接送至芯片的功率管理单元或全局控制逻辑,以触发降频、关断部分电路或完全关机等保护动作。

三、低功耗实现关键

- 亚阈值操作:使传感和偏置电路中的所有MOS管工作在亚阈值区,电流水平可降低至纳安级,这是实现超低静态功耗的核心。

- 简单的结构:避免使用复杂的运放和补偿电路,采用最简化的电流镜、电阻分压和单级比较器,减少晶体管数量和功耗节点。

- 动态关断能力:在过温保护未触发时,可以设计使能信号,周期性地(或由外部事件触发)对温度进行采样,而非持续工作,从而进一步降低平均功耗。

四、仿真与验证

在完成电路设计后,需利用EDA工具(如Cadence Spectre)进行仿真验证。仿真应涵盖:

- 直流温度扫描:验证VPTAT和VREF随温度(如-40°C到150°C)的变化曲线,确保VREF的稳定性以及VPTAT良好的线性度。观察OT_FLAG的翻转点是否精确落在设计温度(如125°C)。

- 功耗分析:在典型工作条件下,测量电路的静态电流,确保其满足低功耗指标(例如小于500nA)。

- 工艺角(Corner)仿真:在TT(典型)、FF(快)、SS(慢)、SF、FS等工艺角以及不同电源电压下进行仿真,验证电路功能的鲁棒性和触发温度的精度(通常要求误差在±10°C以内)。

- 瞬态仿真:模拟温度快速上升的场景,验证电路的响应速度是否满足要求。

五、版图设计注意事项

在物理实现时,版图设计对于保证性能至关重要:

- 匹配性:构成电流镜的MOS管、两个衬底PNP管以及比较器输入对的MOS管必须采用共质心等匹配布局技术,以减小工艺梯度引起的失配。

- 热耦合:温度传感核心单元(PNP管)必须放置在需要被监测热点的附近,确保其感知的温度能真实反映芯片最热区域的温度。

- 噪声隔离:敏感的模拟部分(如偏置和传感单元)应与数字开关电路保持足够距离,并用保护环(Guard Ring)进行隔离,防止衬底噪声干扰。

- 电源走线:为模拟电路提供干净、稳定的电源和地线,避免数字噪声通过电源网络耦合。

结论

本文阐述了一种适用于标准CMOS工艺的低功耗过温保护电路设计方案。该方案利用衬底PNP管和亚阈值偏置技术,在实现精确温度检测的将静态功耗降至极低水平。其结构简单,易于集成,能够有效提升芯片的可靠性和安全性。通过严谨的电路设计、仿真验证和精心的版图布局,可以确保该保护电路在各种工作条件下稳定可靠地运行,为高性能、高可靠性的集成电路产品提供关键保障。

如若转载,请注明出处:http://www.jz876.com/product/17.html

更新时间:2026-05-08 22:20:05