射频、信号处理与集成电路 八大经典电路设计图集锦

在现代电子技术领域,射频电路、信号处理电路与集成电路的设计构成了通信、计算与智能设备的核心。本文将精选并解析八个具有代表性的设计图例,旨在展示其关键原理与应用价值,为工程师与爱好者提供参考。

一、 经典射频功率放大器电路

此设计图展示了基于GaN HEMT器件的C类功率放大器。其核心在于输入/输出匹配网络,通过微带线设计实现阻抗变换,确保在目标频段(如2.4GHz)内获得高功率增益与效率。偏置电路的设计需特别注意稳定性,常包含防自激的电阻衰减网络。该电路是无线发射前端的关键。

二、 低噪声放大器(LNA)射频接收前端

此图聚焦于接收灵敏度的保障。采用低噪声晶体管(如pHEMT),并设计源极负反馈与LC匹配网络,在放大微弱射频信号的将噪声系数降至最低(可低于1dB)。图中清晰标明了直流偏置点和射频扼流圈(RFC)的位置,这是实现高线性度与稳定性的典型结构。

三、 锁相环(PLL)频率合成器

这是一个完整的频率合成系统框图。包含参考晶振、鉴相器(PFD)、电荷泵、环路滤波器、压控振荡器(VCO)以及分频器。设计图清晰地展示了各模块间的信号流向与反馈路径。环路滤波器的RC参数设计尤为关键,决定了频率切换速度与相位噪声性能,广泛应用于射频本地振荡器生成。

四、 超外差式接收机混频器电路

该图详细描绘了利用双平衡混频器(如基于二极管环或Gilbert单元)将射频信号下变频至固定中频的过程。图中标明了本振(LO)输入、射频(RF)输入及中频(IF)输出端口,并配有中频滤波器以抑制镜像干扰。这是实现高选择性接收的经典架构。

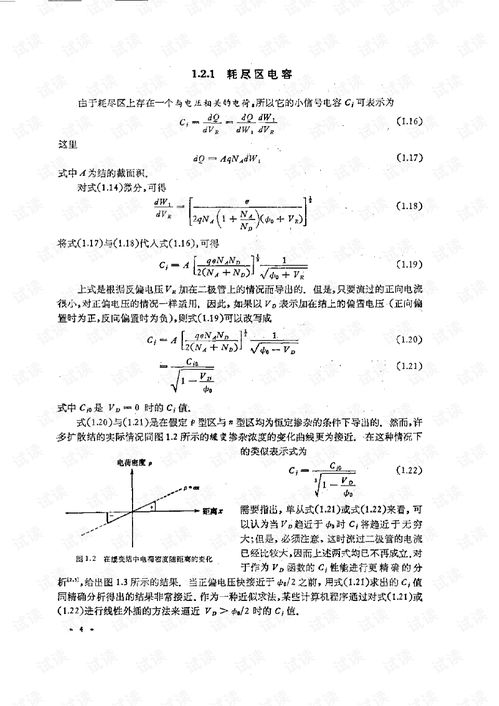

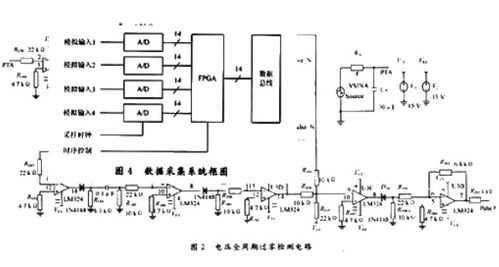

五、 数字中频(IF)采样与处理电路

此设计图体现了从模拟到数字的桥梁。它展示了中频信号经过抗混叠滤波器后,由高速模数转换器(ADC)进行采样。数字下变频(DDC)模块在FPGA或专用芯片中实现,通过数控振荡器(NCO)和乘法器完成,最终输出基带I/Q数字信号流,是现代软件无线电的基础。

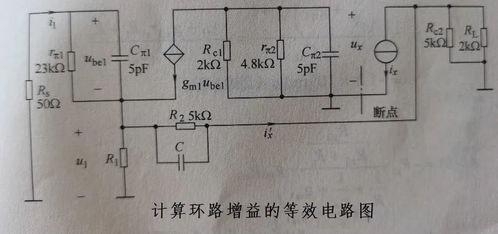

六、 高速运算放大器构成的抗混叠/重建滤波器

这是一个有源滤波器(如多反馈或Sallen-Key拓扑)的详细原理图。图中精确计算并标注了电阻与电容的取值,以实现在特定采样率下所需的截止频率与陡峭的滚降特性。它用于ADC前端的信号调理或DAC后端的平滑输出,是保证信号处理精度的关键模拟电路。

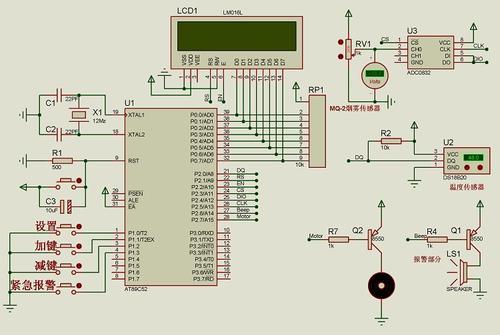

七、 基于标准单元的集成电路版图

此图并非原理图,而是物理实现层面的版图(Layout)示例。它展示了数字标准单元(如与非门、触发器)在芯片上的排列、互连(不同金属层)以及电源/地线网络的规划。图中能清晰看到时钟树布线、电源环和去耦合电容的布局,是连接逻辑设计与芯片制造的蓝图。

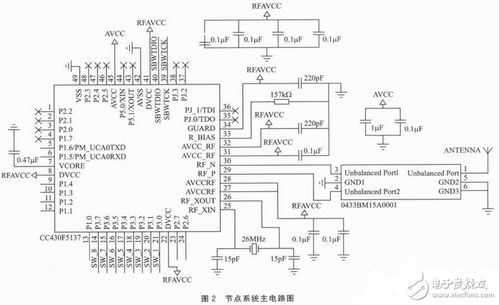

八、 片上系统(SoC)高层次架构框图

此图从系统角度出发,集成了处理器核(CPU/DSP)、数字信号处理模块、内存控制器、高速串行接口(如SerDes)、模拟射频前端接口以及片上互连总线(如AMBA AXI)。框图清晰地划分了数字、模拟和射频域,并标明了关键数据通路,展现了现代集成电路高度集成与协同设计的复杂性与强大功能。

****

从具体的晶体管级射频放大,到抽象的系统级芯片集成,这八大设计图构成了从高频信号产生、变换、处理到数字化与集成化的完整视图。理解这些经典电路图,是掌握现代电子系统设计精髓,并推动通信与计算技术不断向前发展的基石。

如若转载,请注明出处:http://www.jz876.com/product/16.html

更新时间:2026-05-08 06:25:16