集成运放相位补偿电路设计的详细解析

在模拟集成电路设计中,运算放大器(简称运放)是最核心的模块之一,其稳定性直接决定了整个系统的性能。相位补偿是确保运放稳定工作、避免自激振荡的关键技术。本文将深入解析集成运放相位补偿电路的设计原理、常见方法及其在集成电路中的实现考量。

一、相位补偿的必要性:稳定性问题

理想运放的开环增益在很宽的频率范围内保持恒定,但实际运放由多级放大器构成,每级都会引入极点和相移。根据反馈理论,当闭环系统在环路增益为1的频率点(单位增益带宽附近),如果附加相移达到或超过180°,负反馈将转变为正反馈,若此时环路增益仍大于或等于1,电路就会产生自激振荡。因此,相位补偿的核心目标是通过修改运放的频率响应(主要是极点位置),使其在单位增益带宽内满足相位裕度(通常要求大于45°,最佳为60°左右)的要求,从而保证闭环稳定性。

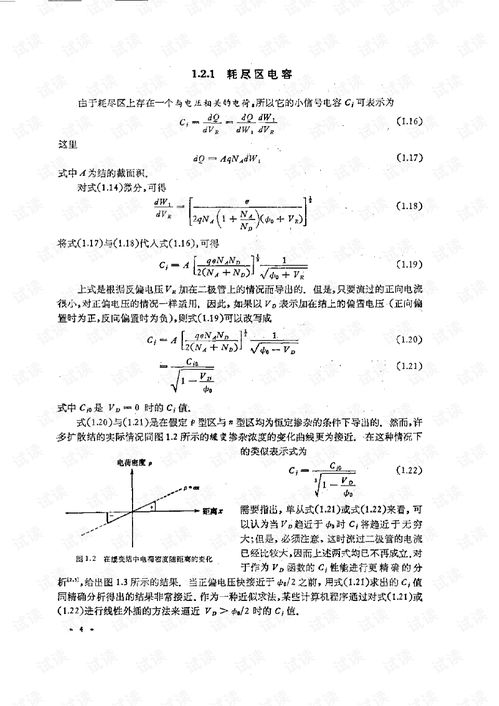

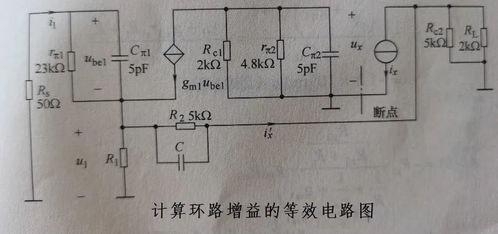

二、相位补偿的基本原理:极点分离与主极点补偿

最经典的补偿思想是“极点分离”。一个未补偿的多级运放通常有多个低频极点。通过在电路中引入补偿电容或电容-电阻网络,可以人为地将最低频率的极点(称为主极点)推向更低的频率,同时将次主极点推向更高的频率,从而在增益降至0dB之前,只经历主极点带来的-90°相移,有足够的相位裕度。

三、集成运放中常见的相位补偿技术

- 密勒补偿:这是最常用且高效的片上补偿方法。在增益级(通常是高增益的第二级)的输入和输出之间跨接一个补偿电容Cc。利用密勒效应,该电容在输入端看到的等效电容被放大了(1+Av)倍,其中Av是该级的增益。这能用较小的物理电容值(节省芯片面积)实现一个很低的主极点频率。密勒补偿会引入一个右半平面的零点,对稳定性有害,需要额外处理。

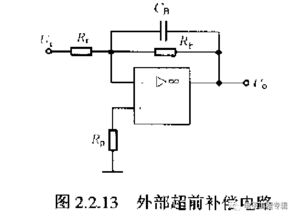

- 前馈补偿:为了消除或抵消密勒电容引入的有害零点,可以采用前馈通路。一种常见方法是在补偿电容Cc上串联一个电阻Rz。通过合理选择Rz的值,可以将右半平面零点推至左半平面甚至无穷远处,或将其移至高频处成为次主极点,从而改善相位裕度。

- 嵌套式密勒补偿:用于三级或更多级的高增益运放。通过精心设计多级之间的补偿电容连接,可以在扩展带宽的同时保持稳定性,但分析和设计更为复杂。

- 负载电容补偿:对于驱动大容性负载的运放,负载电容CL本身会形成一个极点。可以通过在输出级之前引入一个隔离电阻,或采用特殊的输出级结构,将负载电容产生的极点与内部极点分离,避免其破坏稳定性。

四、集成电路设计中的特殊考量

- 面积与功耗的权衡:补偿电容会占用显著的芯片面积。设计者需要在电容值、功耗(与偏置电流和带宽相关)和稳定性之间进行精细优化。采用MOS电容而非多晶硅-扩散电容可以节省面积。

- 工艺偏差与鲁棒性:集成电路制造存在工艺角偏差(Process Corner)。相位补偿设计必须在所有工艺角(快-快、慢-慢、典型)以及不同的温度、电源电压条件下都能保证足够的相位裕度,这需要通过蒙特卡洛仿真等方法来验证。

- 电源抑制比与噪声:补偿网络的引入位置会影响运放的PSRR和噪声性能。例如,密勒电容通常对PSRR有改善作用,但需要仔细评估补偿元件带来的噪声贡献。

- 瞬态响应与建立时间:相位裕度不仅影响稳定性,也直接影响运放的瞬态响应(如过冲、振铃)和小信号建立时间。过度的补偿(相位裕度过大)虽然稳定,但会导致带宽和压摆率下降,建立时间变慢。

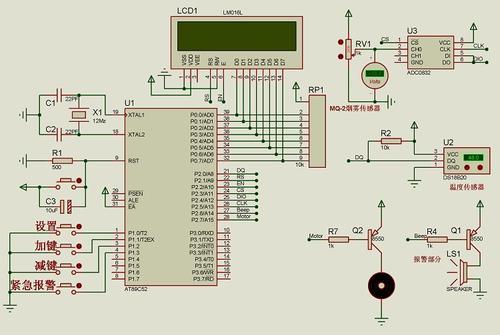

五、设计流程与仿真验证

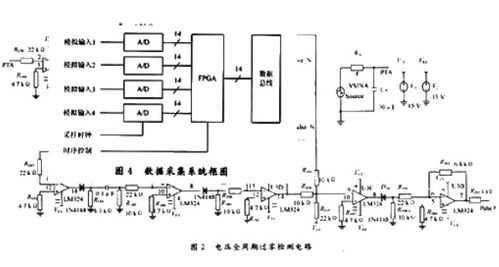

典型的集成运放相位补偿设计流程为:首先根据性能指标(增益、带宽、负载条件)确定运放架构和级数;然后进行初步的交流小信号分析,识别未补偿前的极点/零点位置;接着选择合适的补偿方法,并通过公式进行初步计算确定补偿元件参数;在电路仿真器(如SPICE)中进行深入的交流分析(AC)、瞬态分析(Tran)和稳定性分析(如波特图、相位裕度/增益裕度测量),并跨越各种工艺角和温度进行仿真,迭代优化直至满足所有要求。

,相位补偿是连接运放理论性能与实用稳定性的桥梁。在集成电路设计中,它不是一个独立的步骤,而是与运放的架构选择、功耗预算、面积约束以及整体系统需求紧密交织的关键环节。深入理解其原理并掌握各种补偿技术,是每一位模拟IC设计工程师必备的核心技能。

如若转载,请注明出处:http://www.jz876.com/product/12.html

更新时间:2026-05-08 00:21:21